## How Small Can S-boxes Be?

Chenhao Jia<sup>1</sup>, Tingting Cui<sup>1,3( $\boxtimes$ )</sup>, Qing Ling<sup>1</sup>, Yan He<sup>1</sup>, Kai Hu<sup>2,3,4</sup>, Yu Sun<sup>2</sup> and Meiqin Wang<sup>2,3,4,5</sup>

- <sup>1</sup> School of Cyberspace, Hangzhou Dianzi University, Hangzhou, China

- <sup>2</sup> School of Cyber Science and Technology, Shandong University, Qingdao, China

- <sup>3</sup> Key Laboratory of Cryptologic Technology and Information Security, Ministry of Education, Shandong University, Qingdao, China

- <sup>4</sup> State Key Laboratory of Cryptography and Digital Economy Security, Shandong University, Qingdao, China

- <sup>5</sup> Quancheng Laboratory, Jinan, China

222270059@hdu.edu.cn, cuitingting@hdu.edu.cn, lingqing@hdu.edu.cn, yan\_he@hdu.edu.cn, kai.hu@sdu.edu.cn, yu.sun@mail.sdu.edu.cn, mqwang@sdu.edu.cn

**Abstract.** S-boxes are the most popular nonlinear building blocks used in symmetric-key primitives. Both cryptographic properties and implementation cost of an S-box are crucial for a good cipher design, especially for lightweight ones. This paper aims to determine the exact minimum area of optimal 4-bit S-boxes (whose differential uniform and linearity are both 4) under certain standard cell library. Firstly, we evaluate the upper and lower bounds upon the minimum area of S-boxes, by proposing a Prim-like greedy algorithm and utilizing properties of balanced Boolean functions to construct bijective S-boxes. Secondly, an SAT-aided automatic search tool is proposed that can simultaneously consider multiple cryptographic properties such as the uniform, linearity, algebraic degree, and the implementation costs such as area, and gate depth complexity. Thirdly, thanks to our tool, we manage to find the exact minimum area for different types of 4-bit S-boxes.

The measurement in this paper uses the gate equivalent (GE) as standard unit under UMC 180 nm library, all 2/3/4-input logic gates are taken into consideration. Our results show that the minimum area of optimal 4-bit S-box is 11 GE and the depth is 3. If we do not use the 4-input gates, this minimum area increases to 12 GE and the depth in this case is 4, which is the same if we only use 2-input gates. If we further require that the S-boxes should not have fixed points, the minimum area continue increasing a bit to 12.33 GE while keeping the depth. Interestingly, the same results are also obtained for non-optimal 4-bit bijective S-boxes as long as their differential uniform  $\mathcal{U}(S) < 16$  and linearity  $\mathcal{L}(S) < 8$  (i.e., there is no non-trivial linear structures) if only 2-input and 3-input gates are used. But the minimum area reduce to 9 GE if 4-input gates are involved. More strictly, if we require the algebraic degree of all coordinate functions of optimal S-boxes be 3, the minimum area is 14 GE with fixed point and 14.33 GE without fixed point, and the depth increases sharply to 8

Besides determining the exact minimum area, our tool is also useful to search for a better implementation of existing S-boxes. As a result, we find out an implementation of Keccak's 5-bit S-box with 17 GE. As a contrast, the designer's original circuit has an area of 23.33 GE, while the optimized result by Lu et al. achieves an area of 17.66 GE. Also, we find out the first optimized implementation of SKINNY's 8-bit S-box with 26.67 GE.

**Keywords:** S-box · automatic search · good cryptography properties · minimum area · SAT

Licensed under Creative Commons License CC-BY 4.0.

Received: 2024-09-01 Revised: 2024-11-22 Accepted: 2025-01-23 Published: 2025-03-07

### 1 Introduction

#### 1.1 Background

The substitution box (S-box) is the most widely used building blocks in symmetric-key primitives, including block ciphers, hash functions, authenticated encryptions and message authenticated codes. Security of these primitives heavily depends on the cryptographic properties of their S-boxes, such as the differential uniformity, linearity, algebraic degree, etc, thus choosing an S-box with good cryptographic properties is crucial for cipher designers. On the other hand, the rapid development of the Internet of Things (IoT) prefers ciphers that can be easily deployed in resource-constrained devices, thus the implementation cost of an S-box, such as the area and latency, needs to be as small as possible. To sum up, both the cryptographic properties and implementation cost of S-boxes are important, especially for lightweight ciphers.

There are two active research hotspots about S-boxes: constructing new S-boxes and optimizing existing S-boxes. The former aims to construct an S-box with excellent cryptographic properties but very small implementation cost, while the latter would like to find the smallest implementation cost of an existing S-box. Both research hotspots are challenging, especially for large S-boxes.

Previous effective methods available to construct S-boxes can be mainly classified into 3 types:

- Type 1: choose an S-box from equivalent categories;

- Type 2: construct an S-box by mathematical methods or special structures;

- Type 3: solve out an S-box by automatic tools.

The Type 1 method is only effective for constructing 4-bit S-boxes. In 2007, Leander and Poschman [LP07] defined optimal 4-bit S-boxes according to their ability against differential and linear attacks, and classified all optimal 4-bit S-boxes as 16 categories up to the so-called CCZ equivalence. Many cipher directly uses 4-bit S-boxes from the 16 equivalent categories, such as Serpent [BAK98] and RECTANGLE [ZBL+15]. This classification was further developed by Zhang et al. in [ZBRL15] to 183 categories. In the new classification, Bad-input-Bad-output (BIBO) differential/linear patterns were taken into consideration. Thanks to these classifications, it becomes easy to choose optimal 4-bit S-boxes from different categories as the nonlinear building block of symmetric ciphers. However, the implementation cost is not considered at all. In terms of Type 2 method, combining affine transformations and the inverse function of a finite field to construct S-boxes is a typical mathematical method, just like the S-box used in AES. For sake of S-boxes with low implementation area, some special structures such as Feistel, MISTY, Bridge [LW14, CDL15, TLZ23] as well as cellular automata [MPLJ19, GSP+18] are also widely used. However, these design strategies seriously depend on structures, so it is difficult to reach the minimum area. The Type 3 method, i.e., solving out an S-box by automatic tool, is an interesting and comprehensive method. In [LMC<sup>+</sup>22], Lu et al. proposed an automatic search method based on SAT, which can simultaneously take multiple cryptographic properties into consideration. However, algebraic degree, the very important cryptographic property of S-box, is not covered in this method. Meanwhile, the implementation cost is also not considered yet. Beside that, there are also some explorations on constructing low-depth or low-latency S-boxes[Ras22, TLZ23].

Previous work on optimizing the implementations of existing S-boxes available are few. Jean et al. [JPST17] proposed an automatic tool LIGHTER to search for the circuits with small area for existing S-boxes. They use a graph-based meet-in-the-middle search algorithm under the assumption that every instructions is invertible. Despite of the efficiency and practical applicability for different S-boxes, it is infeasible to prove that their implementation costs are optimal. In FSE 2016, Stoffelen regarded the problem of finding an efficient implementation of a lightweight S-box as a SAT problem [Sto16]. With an

SAT solver, the implementation of an S-box can be solved out with the smallest number of gates. Based on Stoffelen's work, Lu et al. [LWH<sup>+</sup>21] proposed an improved search algorithm and try to find optimized implementations for existing S-boxes with the smallest area under certain standard cell library. However, all previous methods aforementioned are only effective on constructing 4-bit S-boxes and ineffective on larger S-boxes. For example, Lu et al.'s method failed to give an optimal implementation for the 5-bit KECCAK's S-box.

To summarize, there still remain several questions awaiting for answers on designing and optimizing implementation of S-boxes:

- Q1: What is the minimum area of all 4-bit S-boxes, if we would like to design new S-boxes or optimize existing S-boxes under certain standard cell library?

- Q2: How to optimize the implementation for existing n-bit  $(n \ge 5)$  S-boxes with smaller area?

- Q3: How to consider area and depth complexity of an S-box simultaneously when designing new S-boxes and optimizing existing S-boxes?

- Q4: How to cover the requirement on algebraic degree in the automatic search for S-boxes?

In this paper, we aim to propose an improved automatic search method based on SAT to answer these questions.

#### 1.2 Contributions

Since the area cost of different logic gates depends on the technology library, we use the gate equivalent (GE) as the standard unit under the UMC 180nm standard cell library shown in Table 5 to measure and compare the area of S-boxes. The main contributions are briefly summarized as follows:

Propose Prim-like greedy algorithm and properties on balanced Boolean functions to tighten the upper bound and lower bound of the minimum area of S-boxes. Inspired by Prim algorithm in Graph Theory, we transform the process to find the minimum area of S-boxes into a minimum spanning tree problem under some conditions. As an application, to construct an optimal 4-bit S-box, the upper bound of minimum area is 12 GE (8 logic gates) by only using 2-input (or plus 3-input) gates, or 11 GE (6 logic gates) by using 2-input, 3-input and 4-input gates. To find the lower bound of the minimum area of S-boxes, we proposed some properties on balanced Boolean functions, which are helpful to speed up the search process. As a result, we found that it needs at least 9 GE to construct a bijective S-box with  $\mathcal{U}(S) < 16$  and  $\mathcal{L}(S) < 8$  by only using 2-input and 3-input gates. These findings are useful to shrink the possible range of the minimum area of S-box.

Improve the automatic search model for S-boxes in [LMC<sup>+</sup>22] via adding constraints on algebraic degree. Algebraic degree is an important cryptographic property of S-boxes. It can be found from the ANFs of S-box's coordinate functions. However, constructing ANF of a Boolean function is difficult by the truth table in SAT model. In this paper, we overcome this problem by the transformation from SoP expression of Boolean function to ANF expression. Therefore, it becomes able to express every coefficient in ANF and add constraints on algebraic degree within the SAT model.

Improve the automatic search method for optimizing implementation of existing S-boxes in [LWH<sup>+</sup>21] via some acceleration techniques and adding constraints on depth complexity. By utilizing the order-independence of inputs for 2-input and 3-input logic gates, as well as bit-permutation equivalence of S-boxes, the search space can be significantly reduced. Beside that, the requirement on depth complexity can be added into our improved model. As a result, we can search out better implementation

| 8            |      |        |                                                               |          |                  |             |       |

|--------------|------|--------|---------------------------------------------------------------|----------|------------------|-------------|-------|

|              |      |        |                                                               |          | Area (GE         | )           |       |

| S-box        | Size | # Gate | Basis                                                         | LIGHTER  | Stoffelen et al. | Lu et al.   | 0     |

|              |      |        |                                                               | [JPST17] | [Sto16]          | $[LWH^+21]$ | Ours  |

| LBLOCK $S_0$ | 4    | 10     | $\{\mathcal{G}_1,\mathcal{G}_2\}$                             | 16.33    | 23.00            | 16.33       | 16.33 |

| PICCOLO      | 4    | 8      | $\{\mathcal{G}_1,\mathcal{G}_2\}$                             | 13.00    | 16.66            | 13.00       | 13.00 |

| SKINNY-64    | 4    | 8      | $\{\mathcal{G}_1,\mathcal{G}_2\}$                             | 13.33    | 16.33            | 13.33       | 13.33 |

| RECTANGLE    | 4    | 11     | $\{\mathcal{G}_1,\mathcal{G}_2\}$                             | 18.33    | 25.66            | 18.00       | 18.00 |

| RECIANGLE    | 4    | 11     | $\{\mathcal{G}_1,\mathcal{G}_2,\mathcal{G}_3,\mathcal{G}_4\}$ | _        | _                | 17.33       | 17.33 |

| Ours         | 4    | 8      | $\{\mathcal{G}_1,\mathcal{G}_2\}$                             | _        | _                | _           | 12.00 |

| Ours         | 4    | 6      | $\{\mathcal{G}_1,\mathcal{G}_2,\mathcal{G}_3,\mathcal{G}_4\}$ | _        | _                | _           | 11.00 |

| KECCAK       | 5    | 13     | $\{\mathcal{G}_1,\mathcal{G}_2\}$                             | _        | _                | 17.66       | 17.00 |

| SKINNY-128   | 8    | 16     | $\{\mathcal{G}_1,\mathcal{G}_2\}$                             | _        | -                | _           | 26.67 |

**Table 1:** Comparison of the minimum area cost of optimal 4-bit S-Boxes and a few higher-bit S-boxes.

of 5-bit S-box used in KECCAK with smaller area. Meanwhile, we give the optimizing implementation of 8-bit S-box used in SKINNY with smaller area for the first time. The results are summarized in Table 1.

Propose an automatic search model for S-boxes by considering multiple cryptographic properties and implementation area and depth complexity simultaneously based on SAT. In theory, combining the models in [LMC<sup>+</sup>22] and [LWH<sup>+</sup>21] and some slight changes makes it possible to find an S-box satisfying required cryptographic properties and area cost. However, by experiments, we found that the combined model could not be solved out for even 4-bit S-boxes when area cost is restricted as a lower value. In other words, the direct combined model cannot be used to find the minimum area of 4-bit S-boxes. However, based on the first three contributions, we made our model be able to solve the above problem. Specifically, by combining the improved models in the second and third contributions, it is able to determine the minimum area between upper bound and lower bound. Under the minimum area of S-boxes, we can further find the minimum depth. As a result, we apply it on 4-bit S-boxes. If only 2-input and 3-input logic gates are used to construct general bijective 4-bit S-boxes with  $\mathcal{U}(S) < 16$  and  $\mathcal{L}(S) < 8$ , the minimum area is 12 GE with fixed point, as well as 12.33 GE without fixed point. So does optimal 4-bit S-boxes. Under each case above, the depth is at least 4. Furthermore, the minimum area is 14 GE with fixed point, as well as 14.33 GE without fixed point to construct optimal 4-bit S-boxes with all algebraic degree 3 of coordinate functions. Under each case above, the depth is at least 8. If all logic gates including 4-input gates are used to construct optimal 4-bit S-boxes, the minimum area is 11 GE without fixed point, now the gate depth is at least 3. If all logic gates are involved to construct general bijective 4-bit S-boxes, the minimum area is 9 GE, and the gate depth is also at least 3. All results are summarized in Table 2. All source codes of our tool and searched results are available at https://github.com/Chenhao-Jia/Area-Optimized-Implementation-for-S-box.

#### 2 Preliminaries

#### 2.1 Notations

This subsection introduces notations and conceptions used in this paper. Some simple notations are given in Table 3.

A Boolean function is a mapping from  $\mathbb{F}_2^n$  to  $\mathbb{F}_2$ , while a vectorial Boolean function is a mapping from  $\mathbb{F}_2^n$  to  $\mathbb{F}_2^m$ :

$$(x_0, x_1, \dots, x_{n-1}) \mapsto (f_0(x_0, x_1, \dots, x_{n-1}), f_1(x_0, x_1, \dots, x_{n-1}), \dots, f_{m-1}(x_1, x_2, \dots, x_{n-1})),$$

where each  $f_i(x_0, x_1, \dots, x_{n-1})$  is a Boolean function. An S-box with n-bit input and

| Basis                                           | $\mathcal{U}(S)$ | $\mathcal{L}(S)$ | Min $deg(S)$ | Max $deg(S)$ | Without<br>fixed point | Optimal<br>S-box | #Logic<br>gate | Area<br>UMC 180nm   | Area<br>TSMC 65nm  | Minimum<br>area | Depth                                          |

|-------------------------------------------------|------------------|------------------|--------------|--------------|------------------------|------------------|----------------|---------------------|--------------------|-----------------|------------------------------------------------|

|                                                 |                  |                  | 2            | 3            | X                      | ✓                | 8              | 12 GE               | 14 GE              | <b>√</b>        | 4                                              |

|                                                 |                  |                  | 2            | 3            | ✓                      | ✓                | 8              | $12.33~\mathrm{GE}$ | $14.5~\mathrm{GE}$ | ✓               | 4                                              |

|                                                 | 4                | 4                | 3            | 3            | X                      | ✓                | 9              | 14 GE               | 16.5 GE            | <b>√</b>        | 8                                              |

| (0,0)                                           |                  |                  | 3            | 3            | ✓                      | ✓                | 9              | $14.33~\mathrm{GE}$ | $17~\mathrm{GE}$   | ✓               | 8                                              |

| $\{\mathcal{G}_1,\mathcal{G}_2\}$               |                  |                  | 2            | 3            | ×                      | ×                | 8              | 12 GE               | 14 GE              | ✓               | 1 Depth 4 4 8 8                                |

|                                                 | < 16             | < 8              | 2            | 3            | ✓                      | ×                | 8              | $12.33~\mathrm{GE}$ | $14.5~\mathrm{GE}$ | ✓               |                                                |

|                                                 | 10               | < 0              | 2            | 2            | ×                      | ×                | 8              | 12 GE               | 14 GE              | ✓               |                                                |

|                                                 |                  |                  | 2            | 2            | ✓                      | ×                | 8              | $12.33~\mathrm{GE}$ | 14.5  GE           | ✓               | 4                                              |

|                                                 |                  |                  | 2            | 3            | ×                      | ✓                | 8              | 12 GE               | 14 GE              | ✓               | 4                                              |

|                                                 | 4                | 4                | 2            | 3            | ✓                      | ✓                | 8              | $12.33~\mathrm{GE}$ | $14.5~\mathrm{GE}$ | ✓               | 4                                              |

|                                                 | 4                | 4                | 3            | 3            | ×                      | ✓                | 9              | 14 GE               | $16.5~\mathrm{GE}$ | ✓               | 8                                              |

| $\{\mathcal{G}_1,\mathcal{G}_2,\mathcal{G}_3\}$ |                  |                  | 3            | 3            | ✓                      | ✓                | 9              | $14.33~\mathrm{GE}$ | 17  GE             | ✓               | 8                                              |

| (91,92,93)                                      |                  |                  | 2            | 3            | ×                      | ×                | 8              | 12 GE               | 14 GE              | ✓               | 4                                              |

|                                                 | < 16             | < 8              | 2            | 3            | ✓                      | ×                | 8              | $12.33~\mathrm{GE}$ | 14.5  GE           | ✓               | A Depth  4 4 8 8 8 4 4 4 4 4 4 4 4 4 4 4 4 4 4 |

|                                                 | \ 10             | < o              | 2            | 2            | ×                      | ×                | 8              | 12 GE               | 14 GE              | ✓               | 4                                              |

|                                                 |                  |                  | 2            | 2            | ✓                      | ×                | 8              | $12.33~\mathrm{GE}$ | $14.5~\mathrm{GE}$ | ✓               | 4                                              |

| (C, C, C, C, )                                  | 4                | 4                | 2            | 3            | ✓                      | ✓                | 6              | 11 GE               | 13.5 GE            | ✓               | 3                                              |

| $\{G_1, G_2, G_3, G_4\}$                        |                  | -                |              | -            |                        |                  |                | . 07                | 07                 |                 | -                                              |

Table 2: Results on the minimum area cost of three types of S-boxes under the basis  $\{\mathcal{G}_1, \mathcal{G}_2\}, \{\mathcal{G}_1, \mathcal{G}_2, \mathcal{G}_3\} \text{ and } \{\mathcal{G}_1, \mathcal{G}_2, \mathcal{G}_3, \mathcal{G}_4\}.$

**Table 3:** Notations used in this paper.

| $\overline{\mathbb{Z}}_n$ | The finite set $\{0, \dots, n-1\}$ .                                                                                         |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------|

| $\mathbb{F}_2$            | The finite field with only two elements $\{0,1\}$ .                                                                          |

| $\mathbb{F}_2^n$          | The <i>n</i> -dimensional vector space over $\mathbb{F}_2$ .                                                                 |

| $x \oplus y$              | Bitwise exclusive OR of $x$ and $y$                                                                                          |

| $a \wedge b$              | AND of Boolean variable $a$ and $b$ which equals to $ab$ .                                                                   |

| $a \lor b$                | OR of Boolean variable $a$ and $b$ which equals to $ab + a + b$ .                                                            |

| $\neg a$                  | NOT of Boolean variable $a$ which equals to $a + 1$ .                                                                        |

| $\mathcal{G}_1$           | The logic gate set with only 1 input, i.e. $\mathcal{G}_1 = \{NOT\}.$                                                        |

| $\mathcal{G}_2$           | The nonlinear logic gate set with 2 inputs, i.e. $\mathcal{G}_2 = \{AND, NAND, OR, NOR\}.$                                   |

| $\mathcal{G}_3$           | The nonlinear logic gate set with 3 inputs, i.e. $\mathcal{G}_3 = \{AND3, NAND3, OR3, NOR3\}.$                               |

| $\mathcal{G}_4$           | The nonlinear logic gate set with 4 inputs, i.e. $\mathcal{G}_4 = \{MAOI1, MOAI1\}.$                                         |

| $\mathcal{G}l$            | The linear logic gate set except NOT, i.e. $Gl = \{XOR, XNOR\}.$                                                             |

| wt(u)                     | The Hamming weight of $u$ where $u \in \mathbb{F}_2^n$ , $u = (u_0, \dots, u_{n-1})$ .                                       |

| $f(x_0, \dots, x_{n-1})$  | $\mathbb{F}_2$ ) A function mapping $\mathbb{F}_2^n$ to $\mathbb{F}_2$ , also called an <i>n</i> -variable Boolean function. |

| $\langle x, y \rangle$    | The inner product of a and b which equals to $\sum_{i=0}^{n-1} x_i y_i$ .                                                    |

| #{}                       | The number of qualified set elements.                                                                                        |

m-bit output can be represented by such a vectorial Boolean function.

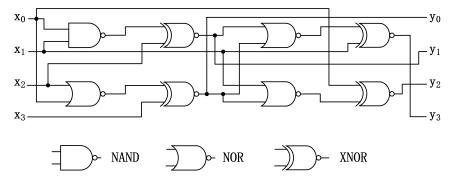

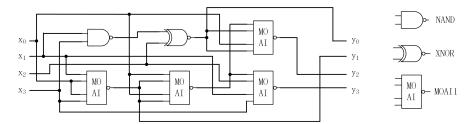

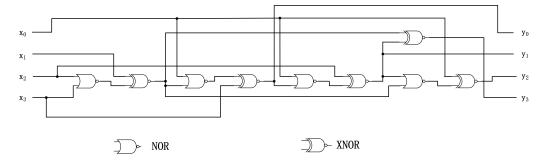

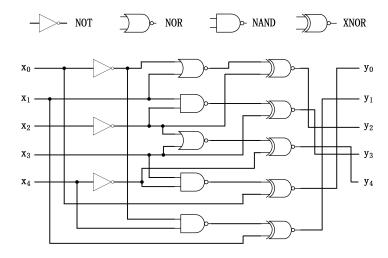

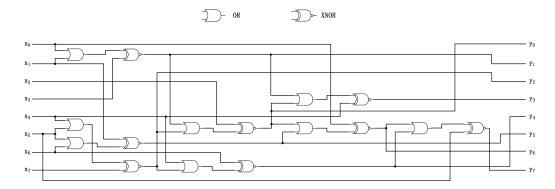

Boolean circuits are defined according to the logic gates they contain. For example, a circuit might contain binary AND and OR gates and unary NOT gates. Each gate corresponds to a small Boolean function that takes a fixed number of bits as input and outputs a single bit. The most common gates used in a circuit are shown in Table 4. This paper considers implementations of S-boxes only with these gates.

#### 2.2 Main Cryptographic Properties for an S-Box

We will first give the definitions of an S-box related to differential cryptanalysis, linear cryptanalysis and various forms of algebraic/cubic cryptanalysis.

**Definition 1** (Differential Distribution Table(DDT)[BS90, BS93]). For a vectorial Boolean function  $S: \mathbb{F}_2^m \to \mathbb{F}_2^n$ , the DDT of S is a  $2^m \times 2^n$  table whose rows correspond to the input difference  $\alpha$  to S and whose columns correspond to the output difference  $\beta$  of S.

$<sup>^1</sup>$  A Boolean variable is regard as a variable over  $\mathbb{F}_2$  in this paper.  $^2$  Unless otherwise specified, + and  $\sum$  in this paper are operations over  $\mathbb{F}_2$ .

| Operation | Function                     | Operation | Function                                                            |

|-----------|------------------------------|-----------|---------------------------------------------------------------------|

| NAND      | $(a,b) \to \neg (a \land b)$ | NAND3     | $(a,b,c) \to \neg (a \land b \land c)$                              |

| NOR       | $(a,b) \to \neg (a \lor b)$  | NOR3      | $(a,b,c) \to \neg (a \lor b \lor c)$                                |

| AND       | $(a,b) \to (a \land b)$      | AND3      | $(a,b,c) \to (a \land b \land c)$                                   |

| OR        | $(a,b) \to (a \lor b)$       | OR3       | $(a,b,c) \to (a \lor b \lor c)$                                     |

| NOT       | $a \rightarrow \neg a$       | MAOI1     | $(a, b, c, d) \rightarrow \neg((a \land b) \lor (\neg(c \lor d)))$  |

| XOR       | $(a,b) \to (a \oplus b)$     | MOAI1     | $(a, b, c, d) \rightarrow \neg((a \lor b) \land (\neg(c \land d)))$ |

| XNOR      | $(a,b) \to \neg(a \oplus b)$ |           |                                                                     |

**Table 4:** Common logic gates and their corresponding expressions in standard cell library

The entry at index  $(\alpha, \beta)$  is

$$\delta_S(\alpha, \beta) := \# \left\{ x \in \mathbb{F}_2^m | S(x) \oplus S(x \oplus \alpha) = \beta \right\}. \tag{1}$$

**Definition 2** (Differential Uniformity[Nyb93]). The differential uniformity of an S-box  $S: \mathbb{F}_2^m \to \mathbb{F}_2^n$  is defined as:

$$\mathcal{U}(S) := \max_{\alpha \in \mathbb{F}_2^n \setminus \{0\}, \beta \in \mathbb{F}_2^n} \delta_S(\alpha, \beta). \tag{2}$$

**Definition 3** (Linear Approximation Table (LAT)[Mat93]). For a vectorial Boolean function  $S: \mathbb{F}_2^m \to \mathbb{F}_2^n$ , the LAT of S is a  $2^m \times 2^n$  table whose rows correspond to the input mask  $\alpha$  to S and whose columns correspond to the output mask  $\beta$  of S. The entry at index  $(\alpha, \beta)$  is

$$LAT_S(\alpha, \beta) := |\lambda_S(\alpha, \beta) - 2^{n-1}|. \tag{3}$$

where  $\lambda_S(\alpha, \beta) = \# \{ x \in \mathbb{F}_2^m | \alpha \cdot x \oplus \beta \cdot S(x) = 0 \}.$

**Definition 4** (Linearity [Mat93]). The linearity of an S-box  $S: \mathbb{F}_2^m \to \mathbb{F}_2^n$  is defined as:

$$\mathcal{L}(S) := \max_{\alpha \in \mathbb{F}_2^m \setminus \{0\}, \beta \in \mathbb{F}_2^n} |LAT_S(\alpha, \beta)|.$$

In [LP07], Leander and Poschmann defined the optimal 4-bit S-boxes as those S-boxes that simultaneously achieve optimal differential uniformity and linearity:

**Definition 5** (Optimal 4-bit S-boxes[LP07]). Let  $S : \mathbb{F}_2^4 \to \mathbb{F}_2^4$  be an S-box. If S fulfills the following conditions, then it is called an optimal 4-bit S-box:

- 1. S is a bijection.

- 2. U(S) = 4.

- 3.  $\mathcal{L}(S) = 4$ .

Saarinen et al. put forward the definition of permutation-xor equivalence in [Saa11]. The algebraic degree, linearity and uniformity are example properties of (vectorial) Boolean functions that are invariant over any of these equivalences. Rasoolzadeh showed that the latency complexity is invariant also under the extended bit permutation equivalence [Ras22]. The definition of bit permutation equivalent is as follows:

**Definition 6** (Bit permutation equivalent [ZBRL15]). Let  $P_1$  and  $P_0$  be two bit permutation matrices. The S-box S' defined by

$$S'(x) = P_0 S(P_1(x))$$

belongs to the permutation-xor equivalence set of  $S, S' \in PE(S)$ .

Thus, the S-boxes within the same bit permutation equivalent class share the same algebraic degree, uniformity, and linearity. Moreover, it is evident that the area and depth complexity of the S-boxes within this class are also identical.

When applying to optimal 4-bit S-boxes, the following theorem formalized as follows.

**Theorem 1.** [LP07] Let S' permutation equivalent to S. If S is an optimal 4-bit S-box, then S' is an optimal 4-bit S-box as well.

In addition to the differential uniformity and linearity, another metric to determine the security of an S-box is the algebraic degree.

**Definition 7** (Algebraic Normal Form (ANF) of a Boolean function and its algebraic degree [CP02, DS09]). A Boolean function  $f: \mathbb{F}_2^n \to \mathbb{F}_2$  can be uniquely represented by an n-variate polynomial over  $\mathbb{F}_2$ , named the algebraic normal form of f:

$$f(x_0, x_1, \dots, x_{n-1}) = \sum_{u \in \mathbb{F}_2^n} \alpha_u \prod_{i=0}^{n-1} x_i^{u_i}, \text{ where } \alpha_u \in \mathbb{F}_2.$$

where  $x_i, u_i$  are the *i*-th bit of x and u, respectively, and  $x_i^{u_i} = x_i$  when  $u_i = 1$  and 1 when  $u_i = 0$ . The algebraic degree  $\deg(f)$  of function f is

$$\deg(f) = \max_{u \in \mathbb{F}_2^n} \{ \operatorname{wt}(u) | \alpha_u \neq 0 \}.$$

**Lemma 1** ([CCH10, LN97]). Let f be an n-variable balanced Boolean function. Then algebraic degree of f is at most n-1.

**Definition 8** (Algebraic Degree of an S-box[LP07]). The algebraic degree of an S-box  $S:(x_0,\dots,x_{n-1})\mapsto (f_0,\dots,f_{m-1})$  is

$$deg(S) = \max_{i} \{ deg(f_i) \}.$$

#### 2.3 Implementation of Boolean Functions

The area and latency are two primary metrics when measuring the hardware implementation cost of an S-box. The area of an S-box is typically measured in terms of gate equivalent (GE). In different libraries GEs of different gates are different. In this paper, we evaluate the area of S-boxes under different standard cell librarys as shown in Table 5. It should be noted that unless specified, we measure the area of S-boxes under UMC 180nm library. Table 5 also provides the area of each gate in the respective libraries.

|              | Tubic 5. O         | Lb Oi                                     | IIICIIIIC   | med gai     | cs in an      | iciciii iii   | orarica     | ٠.         |            |

|--------------|--------------------|-------------------------------------------|-------------|-------------|---------------|---------------|-------------|------------|------------|

| Library      | Gate               | AND<br>OR                                 | NAND<br>NOR | XOR<br>XNOR | NAND3<br>NOR3 | XOR3<br>XNOR3 | NOT         | MAOI1      | l MOAI1    |

| UMC 180nm    | Area (GE)<br>Ratio | 1.33                                      |             | 3.00<br>9   | 1.33<br>4     | $4.67 \\ 14$  | 0.67        | 2.67<br>8  | 2.00<br>6  |

| TSMC 65nm    | Area (GE)<br>Ratio | $\begin{vmatrix} 1.50 \\ 6 \end{vmatrix}$ | 1.00<br>4   | 3.00<br>12  | 1.50<br>6     | 5.50<br>22    | $0.50 \\ 2$ | 2.50<br>10 | 2.50<br>10 |

| Nangate 45nm | Area (GE)<br>Ratio | 1.33                                      | 1.00        | 2.00        | 1.33<br>4     | 4.00<br>12    | 0.67 2      | 2.67       | 2.00       |

**Table 5:** GEs of mentioned gates in different libraries.

It can be seen that, AND and OR gates, as well as XOR gates, have a larger GE plus NOT than their inverse gates at UMC 180nm, so we do not take NOT gates into our

<sup>&</sup>lt;sup>1</sup> The ratio is measured in multiples of  $\frac{1}{3}$  GE as the reference unit.

consideration when pursuing GE minimization. We recall the definitions of *Gate Count Complexity* and *Gate Depth Complexity* to measure the cost of implementing Boolean functions as follows.

**Definition 9** (Gate Count Complexity[Sto16]). The gate count complexity of a Boolean function is defined as the minimum number of logic gates required to implement this function.

Even though different types of gates have different implementation (area) costs, this definition is typically considered the first simplified estimation for the minimum area cost for hardware implementation of a function.

In [Sto16], Stoffelen transformed the problem of searching for hardware and software implementations of S-boxes into a Boolean satisfiability problem for solving. Compared to heuristic algorithms, the model constructed by Stoffelen can be used to search for the minimum number of standard logic gates required for hardware and software implementation of S-boxes, achieving the smallest possible number of standard logic gates used. However, since different standard logic gates have different hardware implementation areas, a circuit with the minimum number of standard logic gates does not necessarily have the minimum area.

**Definition 10** (Gate Depth Complexity[Sto16]). The depth of a circuit is defined as the length of the longest paths from an input gate to an output gate.

In the case of the gate depth complexity, even though different types of gates have different implementation (delay) costs, this definition is usually considered the first estimation for the minimum delay cost for hardware implementation of a function.

## 3 Tight Bounds on Minimum Area to Construct S-boxes

In this section, we first propose a Prim-like greedy algorithm to tighten the upper bound of the minimum area to construct S-boxes with certain cryptographic properties in subsection 3.1. Then, by finding some properties on balanced Boolean functions, the lower bound of minimum area to construct S-boxes is tightened in subsection 3.2.

# 3.1 Upper Bound of Minimum Area to Construct S-boxes under Certain Cryptographic Properties

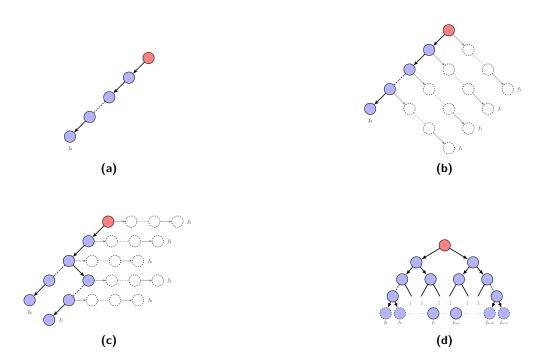

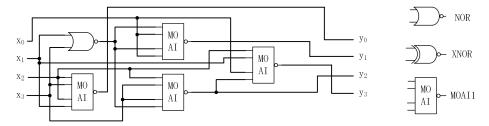

In this part, we concentrate on finding the upper bound on the minimum area for constructing a bijective S-box with differential uniform  $\mathcal{U}(S)$  and linearity  $\mathcal{L}(S)$ . Each S-box coordinate function  $f_i(x)$  is composed of a certain number of logic gates, and meanwhile, different coordinate functions share some gates. To find the minimum area of an S-box is to find the optimal circuit implementation with minimum gate area. Thus, we transform the construction of an S-box into a minimum spanning tree problem under conditions with the help of graph theory. The circuit implementation process of an S-box can be regarded as a weighted diagraph, as shown in Figure 1.

In this diagraph, there are two sets: edge set E and vertex set V. Each edge  $g_i \in E$  means a logic gate, while the weight  $w_i$  of  $g_i$  means the are cost of this gate. The vertexes  $(v_i, v_{i+1})$  on both sides of edge  $g_i$  means the input/output states of corresponding logic gate. It is worth noting that, there may be multiple inputs for a gate. To describe clearly, the vertex  $v_i$  in graph only denotes the input with longest depth. But, in actual search with code,  $v_i$  is stored as an expression  $g_i(x_0, x_i, \dots, x_{n-1}, v_1, \dots, v_{i-1})$ . Finally, the output  $(f_0, \dots, f_{m-1})$  of S is located in some vertexs. To find the minimum area of S-boxes under certain differential uniform  $\mathcal{U}(S)$  and linearity  $\mathcal{L}(S)$  is to find the minimum of  $\sum_{i=1}^n w_i$  in the diagraph to get special  $(f_0, \dots, f_{m-1})$  satisfies Lemma 2 and Lemma 3 as follows.

**Figure 1:** Demo on Prim-like greedy Algorithm

**Lemma 2** ([Ras22]). For an n-bit bijective S-box  $S = (f_0, \ldots, f_{n-1})$  with linearity linearity  $\mathcal{L}(S)$ , each of its component functions, namely  $\langle \alpha, S \rangle$  with any  $\alpha \in \mathbb{F}_2^n \setminus \{0\}$ , is balanced and has a linearity of at most  $\mathcal{L}(S)$ .

Using Lemma 2 makes it possible to filter out some of the possibilities, only by having some of the coordinate functions. Precisely, assume that  $f_0$  and  $f_1$  are already chosen, then without choosing other coordinate functions, we can check for balancedness and linearity of  $f_0 \oplus f_1$ . If  $f_0 \oplus f_1$  is balanced and has a linearity at most  $\ell$ , then we choose the third coordinate function,  $f_2$ . Again, we can check for balancedness and linearity of  $f_0 \oplus f_2$ ,  $f_1 \oplus f_2$ , and  $f_0 \oplus f_1 \oplus f_2$ . Continuing in this way, after choosing the last coordinate function,  $f_{n-1}$ , we can check for balancedness and linearity of other  $2^{n-1} - 1$  component functions. If these  $2^{n-1} - 1$  conditions are met, then we have a bijective S-box with linearity at most  $\ell$

**Lemma 3** ([Ras22]). For an n-bit S-box  $S = (f_0, \ldots, f_{n-1})$  with differential uniform  $\mathcal{U}(S)$ , the differential uniformity of sub-S-box  $S'_i = (f_0, \ldots, f_i)$  with i < n is upper bounded by  $\min\{\mathcal{U}(S) \cdot 2^{n-i-1}, 2^n\}$ .

Lemma 3 can also be used to filter out coordinate functions that meet the differential uniformity requirement for the sub-S-box  $S'_i = (f_0, f_1, \dots, f_i)$ .

Next, we illustrate the algorithm to find the minimum of  $\sum_{i=1}^{n} w_i$  meeting certain differential uniform and linearity with the help of Lemma 2 and Lemma 3, which is shown in Algorithm 1. Inspired by Prim algorithm in graph theory, we construct the coordinate functions of an S-box one by one to achieve local optimization. At the very begin, we build a pre-computation table T[cost] to store all combinations of logic gates, indexing by area cost as shown in Table 6. Please note that the combinations in this table are ordered by the number of used gates.

In detail, to construct the first coordinate function  $f_0$ , the steps are as follows.

• Step 1: Try the combination of logic gates from pre-computation T[cost] successively according to area cost. Assume the current combination of logic gates is  $\mathcal{I}_{f_0}$ , and

Algorithm 1: Prim-like greedy Algorithm to achieve the locally minimum solution for area cost.

```

Input: n, \mathcal{G}, V

Output: Cost

1 V^0, \ldots, V^{n-1} \leftarrow \emptyset;

2 V_y = \emptyset;

з global Cost, Cost' = 0;

4 global iter = -1;

5 Function FindingLocalMinimumArea(n, \mathcal{G}, V):

iter++;

for i = 3, 4, 5... do

7

if count = 0 then

8

for k = 1 to \lfloor i/3 \rfloor do

9

10

if count = 0 then

for g_0, \ldots, g_{k-1} \in \mathcal{G} and \sum_{j=0}^{k-1} |g_j| = i do \mid V^{iter} = V;

11

12

for v_0, \ldots, v_{n-1} \ (n=2,3,4) \in V^{iter} \ \mathbf{do}

13

14

if \{\alpha \in \mathbb{F}_2^{iter+1} \setminus \{0\} | \langle \alpha, V_y \cup t_{k-1} \rangle \} is balanced && \mathcal{L}(V_y \cup t_{k-1})

15

t_{k-1}) \leq \mathcal{L}(S) then

if \mathcal{U}(V_y \cup t_{k-1}) \leq \min\{u \cdot 2^{n-iter-1}, 2^n\} then V \leftarrow V \cup V^{iter}, \ V_y \leftarrow V_y \cup t_{k-1};

16

17

count + +;

18

if iter \leq n-1 then

FindingLocalMinimumArea (n, \mathcal{G}, V);

20

break

21

return

23 Cost = Cost'/3

```

**Table 6:** Precomputed table for gate combinations.

| cost(GE)               | combinations of logic gates                        | # combinations |

|------------------------|----------------------------------------------------|----------------|

| $1/3 \times 1$         | Ø                                                  | 0              |

| $1/3 \times 2$         | {NOT}                                              | 1              |

| :                      | :                                                  | i i            |

| $\boxed{1/3 \times 5}$ | {NOT, NAND}, {NOT, NOR}<br>{NAND, NOT}, {NOR, NOT} | 4              |

| <u>:</u>               |                                                    | :              |

the number of logic gates used in  $\mathcal{I}_{f_0}$  is  $|\mathcal{I}_{f_0}|$ :

$$\mathcal{I}_{f_0}: v_0 \xrightarrow{g_0} v_1 \xrightarrow{g_1} \cdots \xrightarrow{g_{|\mathcal{I}_{f_0}|-2}} v_{|\mathcal{I}_{f_0}|-1} = f_0(x_0, \cdots, x_{n-1}), \tag{4}$$

where  $v_0$  is the initial vertex, and  $v_{|\mathcal{I}_{f_0}|-1}$  is the final vertex.

- Step 2: Try possible inputs of gate  $g_0$  from initial input set  $V = \{x_0, \dots, x_{n-1}\}$ , possible inputs of gate  $g_1$  from  $V \cup \{v_1\}, \dots$ , possible inputs of gate  $g_{|\mathcal{I}_{f_0}|-1}$  from  $V \cup \{v_1, v_2, \dots, v_{|\mathcal{I}_{f_0}|-2}\}$ .

- Step 3: Check if  $v_{|\mathcal{I}_{f_0}|-1} = f_0(x_0, \dots, x_{n-1})$  satisfies Lemma 2 and Lemma 3. If so, continue to construct the next coordinate function. Otherwise, return back to Step 2 and Step 1.

This process is shown in Figure 1(a). Now the area cost is  $\sum_{i=0}^{|\mathcal{I}_{f_0}|-1} w_i$ .

To construct the second coordinate function  $f_1$  is slightly different with the process to construct  $f_0$ . The steps are as follows:

• Step 1: Try the combination of logic gates from the pre-computation table T[cost] successively according to area cost. Assume the current combination of logic gates is  $\mathcal{I}_{f_1}$ , and the number of logic gates used in  $\mathcal{I}_{f_1}$  is  $|\mathcal{I}_{f_1}|$ :

$$\mathcal{I}_{f_1}: v_0' \xrightarrow{g_{|\mathcal{I}_{f_0}|}} v_{|\mathcal{I}_{f_0}|} \xrightarrow{g_{|\mathcal{I}_{f_0}|+1}} v_{|\mathcal{I}_{f_0}|+1} \to \cdots \to v_{|\mathcal{I}_{f_0}|+|\mathcal{I}_{f_1}|-1} = f_1(x_0, \cdots, x_{n-1}).$$

(5)

- Step 2: Choose initial vertex  $v_0'$  from set  $\mathcal{V} = \{v_0, v_1, \cdots, v_{|\mathcal{I}_{f_0}|-1}\}$  one by one.

- Step 3: Assume the current  $v_0' = v_i$ ,  $0 \le i \le |\mathcal{I}_{f_0}| 1$ . Try possible inputs of gate  $g_{|\mathcal{I}_{f_0}|}$  from initial input set  $V = \{x_0, \cdots, x_{n-1}, v_0, \cdots, v_i\}$ , possible inputs of gate  $g_{|\mathcal{I}_{f_0}|+1}$  from  $V \cup \{v_{|\mathcal{I}_{f_0}|}\}$ , ..., possible inputs of gate  $g_{|\mathcal{I}_{f_0}|+|\mathcal{I}_{f_1}|-1}$  from  $V \cup \{v_{|\mathcal{I}_{f_0}|}, v_{|\mathcal{I}_{f_0}|+1}, \cdots, v_{|\mathcal{I}_{f_0}|+|\mathcal{I}_{f_1}|-2}\}$ .

- Step 4: Check if  $v_{|\mathcal{I}_{f_0}|+|\mathcal{I}_{f_1}|-1}=f_1(x_0,\cdots,x_{n-1})$  satisfies Lemma 2 and Lemma 3. If so, continue to construct the next coordinate function. Otherwise, return back to Step 3, Step 2 and Step 1.

This Process is shown in Figure 1(b). Now the area cost  $\sum_{i=0}^{|\mathcal{I}_{f_0}|-1} w_i + \sum_{i=0}^{|\mathcal{I}_{f_1}|-1} w_{|\mathcal{I}_{f_0}|+i}$ .

To construct the other coordinate functions  $f_2, \dots, f_{n-1}$  sequentially is similar to the process to construct  $f_1$ . But the difference lies in that the initial vertex set  $\mathcal{V}$  and the input set V would be changed and larger. The process is shown in Figure 1(c)(d). In the end, the total area cost is  $\sum_{i=0}^{|\mathcal{I}_{f_0}|+|\mathcal{I}_{f_1}|+\dots+|\mathcal{I}_{f_{n-1}}|-1} w_i$ .

Application to 4-bit S-boxes. We apply Algorithm 1 on 4-bit S-boxes with both differential uniformity and linearity as 4. By using different sets of logic gates, we get different upper bound of minimum area of 4-bit S-boxes under UMC 180nm library. When we only use 2-input logic gates from  $\mathcal{G}_2$ , the minimum area of S-boxes we found is 12 GE, composed of 8 logic gates. When we use 2-input and 3-input logic gates from  $\{\mathcal{G}_2, \mathcal{G}_3\}$ , the minimum area of S-boxes we found is 12 GE, composed of 8 logic gates. When we use 2-input, 3-input and 4-input logic gates from  $\{\mathcal{G}_2, \mathcal{G}_3, \mathcal{G}_4\}$  together, the minimum area of S-boxes we found is 11 GE, composed of 6 logic gates. The results are summarized in Table 7.

| $\mathcal{U}(S)$ | $\mathcal{L}(S)$ | basis                                           | #logic gate | area (GE) |

|------------------|------------------|-------------------------------------------------|-------------|-----------|

| 4                | 4                | $\{\mathcal{G}_2\}$                             | 8           | 12        |

| 4                | 4                | $\{\mathcal{G}_2,\mathcal{G}_3\}$               | 8           | 12        |

| 4                | 4                | $\{\mathcal{G}_2,\mathcal{G}_3,\mathcal{G}_4\}$ | 6           | 11        |

**Table 7:** Upper bound of minimum area of optimal 4-bit S-boxes under UMC 180nm library

#### 3.2 Lower Bound of Minimum Area to Construct Bijective S-boxes

In this part, we try to seek the lower bound of the minimum area to construct a bijective S-box based on the balanced property of Boolean functions. By default, the algebraic degree of each coordinate function of the S-box should be no less than 2.

Firstly, we propose some properties to real how to construct balanced Boolean functions implemented by logic gates with 2 or 3 inputs.

**Property 1.** If f is an n-variables Boolean function with algebraic degree  $l(l \ge 2)$  obtained by logic gate g, i.e.  $f: V \xrightarrow{g} t = f(V = \{x_0, \dots, x_{n-1}\})$ , where g is a logic gate involved in this paper except  $\mathcal{G}_1 \cup \mathcal{G}_4$  (i.e.  $g \in (\mathcal{G}l \cup \mathcal{G}_2 \cup \mathcal{G}_3)$ ), then  $f(x_0, \dots, x_{n-1})$  is not balanced.

*Proof.* Suppose that  $f(x_0, \dots, x_{n-1})$  is a balanced Boolean function obtained by logic gate g in  $(\mathcal{G}l \cup \mathcal{G}_2 \cup \mathcal{G}_3)$ .

**Case 1.** The gate g is in  $\mathcal{G}l$ . Obviously, the Boolean function expression of gate g would be  $g(x_i, x_j) = x_i + x_j$  or  $g(x_i, x_j) = x_i + x_j + 1$ . Thus, deg(f) = deg(g) = 1 which contradicts the algebraic degree of f being greater than or equal to 2.

Case 2. The gate g is not in  $\mathcal{G}l$ . According to the expressions of the logic gates given in Table 4, we have Boolean function expressions of gate  $g^2$  in  $\mathcal{G}_2$  and gate  $g^3$  in  $\mathcal{G}_3$  as shown in Equation 6 and 7 respectively.

$$g^{2}(x_{i}, x_{j}) = x_{i}x_{j} + \lambda_{1}(x_{i} + x_{j}) + \lambda_{0},$$

(6)

$$g^{3}(x_{i}, x_{j}, x_{k}) = x_{i}x_{j}x_{k} + \lambda_{1}(x_{i}x_{j} + x_{i}x_{k} + x_{j}x_{k} + x_{i} + x_{j} + x_{k}) + \lambda_{0},$$

(7)

where  $\lambda_0$  and  $\lambda_1$  are constants with values of 0 or 1 and  $x_i, x_j, x_k \in \mathbb{F}_2$ . Obviously,  $g^2(x_i, x_j)$  is a binary Boolean function about variables  $x_i$  and  $x_j$ , and its leading term is  $x_i x_j$ , i.e.  $deg(g^2(x_i, x_j)) = 2$ . According to Lemma 1,  $g^2(x_i, x_j)$  is not a balanced Boolean function. Similarly,  $g^3(x_i, x_j, x_k)$  is also not a balanced Boolean function. Thus, whether  $g = g^2$  or  $g = g^3$ , g is unbalanced.

Therefore,  $f(x_0, \dots, x_{n-1})$  with algebraic degree  $l(l \ge 2)$  obtained by logic gate g is not a balanced Boolean function.

**Property 2.** The function  $f(x_0, \dots, x_{n-1})$  is an n-variable balanced Boolean function with algebraic degree  $l(l \geq 2)$  obtained by the composite use of logic gates  $g_0$  and  $g_1$ , i.e.  $f: V \xrightarrow{g_0} t_0 \xrightarrow{g_1} t_1 = f(V = \{x_0, \dots, x_{n-1}\})$ , where  $g_0$  and  $g_1$  are logic gates involved in this paper except  $\mathcal{G}_1 \cup \mathcal{G}_4$  and the output  $t_0$  of  $g_0$  is an input of  $g_1$ , if and only if  $g_0$  is a nonlinear gate and  $g_1$  is a linear gate.

*Proof.* Denote  $t_0$  and  $t_1$  as the outputs of  $g_0$  and  $g_1$  respectively. There are four cases below.

Case 1. The gate  $g_0$  and  $g_1$  are both in  $\mathcal{G}l$ . Obviously, the Boolean function expression of gate g would be  $g_1(t_0) = t_0 + 1$  or  $g_1(t_0, x_i) = t_0 + x_i$  or  $g_1(t_0, x_i) = t_0 + x_i + 1$ . By the proof of Property 1, we have  $deg(f) = deg(g_1) = deg(t_0) = 1$  which contradicts the algebraic degree of f being greater than or equal to 2.

Case 2. The gate  $g_0$  is in  $\mathcal{G}l$  and  $g_1$  is in  $\mathcal{G}_2 \cup \mathcal{G}_3$ . It is clear that  $t_0 = g_0(x_i, x_j) = x_i + x_j$  or  $t_0 = g_0(x_i, x_j) = x_i + x_j + 1$  and  $Pr(t_0 = 0) = \frac{1}{2}$ . Depending on the number of inputs to  $g_1$ , there are two subcases.

**Subcase 1.** The gate  $g_1$  is in  $\mathcal{G}_2$ . According to Equation 6, we have

$$t_1 = g^2(t_0, x_i) = t_0 x_i + \lambda_1(t_0 + x_i) + \lambda_0 = \begin{cases} (\lambda_1 + 1)x_i + \lambda_1 + \lambda_0 & t_0 = 1\\ \lambda_1 x_i + \lambda_0 & t_0 = 0. \end{cases}$$

Since the value of  $t_0$  is determined by two input variables, whether there is a dependency between  $t_0$  and  $x_i$ , we have  $0 < Pr(x_i = u | t_0 = v) < 1$  where  $u, v \in \{0, 1\}$ . Thus

$$Pr(t_{1} = 0) = Pr(t_{0} = 1) \cdot Pr((\lambda_{1} + 1)x_{i} + \lambda_{1} + \lambda_{0} = 0)$$

$$+ Pr(t_{0} = 0) \cdot Pr(\lambda_{1}x_{i} + \lambda_{0} = 0)$$

$$= \begin{cases} \frac{1}{2}Pr(x_{i} = 0|t_{0} = 1) + \frac{1}{2} & \lambda_{1} = 0, \lambda_{0} = 0\\ \frac{1}{2}Pr(x_{i} = 1|t_{0} = 1) & \lambda_{1} = 0, \lambda_{0} = 1\\ \frac{1}{2}Pr(x_{i} = 0|t_{0} = 0) & \lambda_{1} = 1, \lambda_{0} = 0\\ \frac{1}{2} + \frac{1}{2}Pr(x_{i} = 1|t_{0} = 0) & \lambda_{1} = 1, \lambda_{0} = 1 \end{cases}$$

$$\neq \frac{1}{2}.$$

(8)

**Subcase 2.** The gate  $g_1$  is in  $\mathcal{G}_3$ . According to Equation 6, we have

$$t_{1} = g^{3}(t_{0}, x_{i}, x_{j}) = t_{0}x_{i}x_{j} + \lambda_{1}(t_{0}x_{i} + t_{0}x_{j} + x_{i}x_{j} + t_{0} + x_{i} + x_{j}) + \lambda_{0}$$

$$= \begin{cases} t_{0}x_{i} + \lambda_{1}(t_{0} + x_{i}) + \lambda_{0} & x_{i} = x_{j} \\ \lambda_{1} + \lambda_{0} & x_{i} \neq x_{j}. \end{cases}$$

(9)

Thus

$$Pr(t_{1} = 0) = Pr(x_{i} = x_{j}) \cdot Pr(t_{0}x_{i} + \lambda_{1}(t_{0} + x_{i}) + \lambda_{0} = 0) + Pr(x_{i} \neq x_{j}) \cdot Pr(\lambda_{1} + \lambda_{0} = 0) = \begin{cases} \frac{1}{2}Pr(t_{0}x_{i} + \lambda_{1}(t_{0} + x_{i}) + \lambda_{0} = 0 | x_{i} = x_{j}) + \frac{1}{2} & \lambda_{1} + \lambda_{0} = 0 \\ \frac{1}{2}Pr(t_{0}x_{i} + \lambda_{1}(t_{0} + x_{i}) + \lambda_{0} = 0 | x_{i} = x_{j}) & \lambda_{1} + \lambda_{0} \neq 0 \end{cases}$$

$$(10)$$

Similar to **Subcase 1**, the value of  $t_0$  is determined by two input variables, thus we can obtain that  $0 < Pr(t_0x_i + \lambda_1(t_0 + x_i) + \lambda_0 = 0 | x_i = x_j) < 1$  whether there is a dependency between  $t_0$  and  $x_i$ . Therefore,

$$Pr(t_1 = 0) \neq \frac{1}{2}. (11)$$

By Equation 8 and 11, we have  $Pr(t_1 = 0) \neq \frac{1}{2}$  when the gate  $g_0$  is in  $\mathcal{G}l$  and  $g_1$  is in  $\mathcal{G}_2 \cup \mathcal{G}_3$ . Since  $f(x_0, \dots, x_n) = t_1$ , f is not a balanced Boolean function when the gate  $g_0$  is in  $\mathcal{G}l$  and  $g_1$  is in  $\mathcal{G}_2 \cup \mathcal{G}_3$ .

**Case 3.** The gate  $g_0$  and  $g_1$  are both in  $\mathcal{G}_2 \cup \mathcal{G}_3$ . Obviously, by the proof of Property 1,  $Pr(t_0 = 0) \neq \frac{1}{2}$ . Depending on the number of inputs to  $g_1$ , there are two subcases.

**Subcase 1.** The gate  $g_1$  is in  $\mathcal{G}_2$ . According to Equation 6, we have

$$t_1 = g^2(t_0, x_i) = t_0 x_i + \lambda_1(t_0 + x_i) + \lambda_0 = \begin{cases} (\lambda_1 + 1)t_0 + \lambda_1 + \lambda_0 & x_i = 1\\ \lambda_1 t_0 + \lambda_0 & x_i = 0. \end{cases}$$

Note that, whether there is a dependency between  $t_0$  and  $x_i$ , we have  $0 < Pr(t_0 = u | x_i =$

v) < 1 where  $u, v \in 0, 1$ . Thus,

$$Pr(t_{1} = 0) = Pr(x_{i} = 1) \cdot Pr((\lambda_{1} + 1)t_{0} + \lambda_{1} + \lambda_{0} = 0)$$

$$+ Pr(x_{i} = 0) \cdot Pr(\lambda_{1}t_{0} + \lambda_{0} = 0)$$

$$= \begin{cases} \frac{1}{2}Pr(t_{0} = 0|x_{i} = 1) + \frac{1}{2} & \lambda_{1} = 0, \lambda_{0} = 0\\ \frac{1}{2}Pr(t_{0} = 1|x_{i} = 1) & \lambda_{1} = 0, \lambda_{0} = 1\\ \frac{1}{2}Pr(t_{0} = 0|x_{i} = 0) & \lambda_{1} = 1, \lambda_{0} = 0\\ \frac{1}{2} + \frac{1}{2}Pr(t_{0} = 1|x_{i} = 0) & \lambda_{1} = 1, \lambda_{0} = 1 \end{cases}$$

$$\neq \frac{1}{2}$$

$$(12)$$

**Subcase 2.** The gate  $g_1$  is in  $\mathcal{G}_3$ . According to Equation 7, we have

$$t_{1} = g^{3}(t_{0}, x_{i}, x_{j}) = t_{0}x_{i}x_{j} + \lambda_{1}(t_{0}x_{i} + t_{0}x_{j} + x_{i}x_{j} + t_{0} + x_{i} + x_{j}) + \lambda_{0}$$

$$= \begin{cases} t_{0}x_{i} + \lambda_{1}(t_{0} + x_{i}) + \lambda_{0} & x_{i} = x_{j} \\ \lambda_{1} + \lambda_{0} & x_{i} \neq x_{j}. \end{cases}$$

(13)

Thus,

$$Pr(t_{1} = 0) = Pr(x_{i} = x_{j}) \cdot Pr(t_{0}x_{i} + \lambda_{1}(t_{0} + x_{i}) + \lambda_{0} = 0)$$

$$+ Pr(x_{i} \neq x_{j}) \cdot Pr(\lambda_{1} + \lambda_{0} = 0)$$

$$= \begin{cases} \frac{1}{2}Pr(t_{0}x_{i} + \lambda_{1}(t_{0} + x_{i}) + \lambda_{0} = 0 | x_{i} = x_{j}) + \frac{1}{2} & \lambda_{1} + \lambda_{0} = 0 \\ \frac{1}{2}Pr(t_{0}x_{i} + \lambda_{1}(t_{0} + x_{i}) + \lambda_{0} = 0 | x_{i} = x_{j}) & \lambda_{1} + \lambda_{0} \neq 0 \end{cases}$$

$$(14)$$

About the value of  $Pr(t_0x_i + \lambda_1(t_0 + x_i) + \lambda_0 = 0 | x_i = x_j)$ , we can obtain that it is greater than 0 and less than 1 by the former case. Therefore,

$$Pr(t_1 = 0) \neq \frac{1}{2}. (15)$$

By Equation 8 and 15, we have  $Pr(t_1 = 0) \neq \frac{1}{2}$  when the gate  $g_0$  and  $g_1$  are both in  $\mathcal{G}_2 \cup \mathcal{G}_3$ . Since  $f(x_0, \dots, x_n) = t_1$ , f is not a balanced Boolean function when the gate  $g_0$  and  $g_1$  are both in  $\mathcal{G}_2 \cup \mathcal{G}_3$ .

**Case 4.** The gate  $g_0$  is in  $\mathcal{G}_2 \cup \mathcal{G}_3$  and  $g_1$  is in  $\mathcal{G}l$ . There does exist some  $g_0$  and  $g_1$  such that f is balanced, e.g.,

$$t_0 = g_0(x_i, x_j) = x_i x_j, t_1 = g_1(t_0, x_k) = t_0 + x_k, f(x_0, \dots, x_{n-1}) = t_1 = g_1(t_0, x_k) = t_0 + x_k = x_i x_j + x_k,$$

(16)

where  $0 \le i, j, k < n, i \ne j, i \ne k$  and  $j \ne k$ . Obviously,

$$Pr(f=0) = Pr(t_1=0) = Pr(x_k=0) \cdot Pr(x_i x_j=0) + Pr(x_k=0) \cdot (1 - Pr(x_i x_j=0)) = \frac{1}{2}.$$

Thus, f is indeed a balanced Boolean function.

In sum, f is balanced Boolean function if and only if  $g_0$  is a nonlinear gate and  $g_1$  is a linear gate.

From the above properties, according to the cost of logic gates in Table 5, it takes at least 3 GE to achieve a balanced Boolean function with an algebraic degree of at least 2.

We define "continuous composite use of logic gates" as the case that the output of the previous gate is the input of the next gate like a chain. Then we propose the following property.

**Property 3.** Let  $f(x_0, \dots, x_{n-1})$  is an n-variable Boolean function with algebraic degree  $l(l \geq 2)$  obtained by  $\widetilde{g}$  and  $g_1$ , i.e.  $f: V \xrightarrow{\widetilde{g}} t_m \xrightarrow{g_1} t_{m+1} = f(V = \{x_0, \dots, x_{n-1}\})$ , where  $\widetilde{g}$  is some continuous composite use of logic gates except  $\mathcal{G}_1 \cup \mathcal{G}_4$ ,  $g_1$  is a nonlinear logic gate with 2 inputs, and the output  $t_m$  of  $\widetilde{g}$  is an input of  $g_1$ . If  $t_m$  is the first balanced output among the outputs of the logic gates used in  $\widetilde{g}$ , then f is not a balanced Boolean function.

*Proof.* Since  $t_m$  reaches an balanced state, we have  $Pr(t_m = 0) = \frac{1}{2}$ . Since the gate  $g_1$  is in  $\mathcal{G}_2$ , according to Equation 6, we have

$$t_{m+1} = g^2(t_m, t_s) = t_m t_s + \lambda_1(t_m + t_s) + \lambda_0 = \begin{cases} (\lambda_1 + 1)t_s + \lambda_1 + \lambda_0 & t_m = 1\\ \lambda_1 t_s + \lambda_0 & t_m = 0. \end{cases}$$

where  $t_s$  is one of the outputs of the logic gates used in  $\tilde{g}$  or directly belongs to V. And

$$Pr(t_{m+1} = 0) = Pr(t_m = 1) \cdot Pr((\lambda_1 + 1)t_s + \lambda_1 + \lambda_0 = 0) + Pr(t_m = 0) \cdot Pr(\lambda_1 t_s + \lambda_0 = 0)$$

$$= \begin{cases} \frac{1}{2}Pr(t_s = 0|t_m = 1) + \frac{1}{2} & \lambda_1 = 0, \lambda_0 = 0 \\ \frac{1}{2}Pr(t_s = 1|t_m = 1) & \lambda_1 = 0, \lambda_0 = 1 \\ \frac{1}{2}Pr(t_s = 0|t_m = 0) & \lambda_1 = 1, \lambda_0 = 0 \\ \frac{1}{2} + \frac{1}{2}Pr(t_s = 1|t_m = 0) & \lambda_1 = 1, \lambda_0 = 1. \end{cases}$$

$$(17)$$

When  $t_s$  is one of the outputs of the logic gates used in  $\tilde{g}$ ,  $Pr(t_s = 0) \neq \frac{1}{2}$ . Since  $\tilde{g}$  is some continuous composite use of logic gates,  $t_m$  can be regarded as the output of  $t_s$  as an input through the continuous composite use of logic gates. On the other hand,

$$Pr(t_m = u) = Pr(t_s = 0, t_m = u) + Pr(t_s = 1, t_m = u)$$

$$= Pr(t_m = u | t_s = 0) Pr(t_s = 0) + Pr(t_m = u | t_s = 1) Pr(t_s = 1) = \frac{1}{2}, u = 0, 1.$$

(18)

If  $Pr(t_s=0,t_m=u)=0$ , then  $Pr(t_m=u)=Pr(t_m=u|t_s=1)Pr(t_s=1)\leq Pr(t_s=1)<\frac{1}{2}$ , which is in contradiction with  $Pr(t_m=0)=\frac{1}{2}$ . Thus,  $Pr(t_s=0,t_m=u)\neq 0$ . Similarly,  $Pr(t_s=1,t_m=u)\neq 0$ . Therefore,  $0< Pr(t_s=0,t_m=u)<1$  and  $0< Pr(t_s=1,t_m=u)<1$ . Furthermore,  $0< Pr(t_s=u|t_m=v)<1$  where  $u,v\in 0,1$ . According to Equation 17, we have  $Pr(t_{m+1})\neq \frac{1}{2}$ . Then we have f is not a balanced function

When  $t_s \in V$ , then the case become **Case 2.** in Property 2 and we have f is not a balanced function.

In sum,

$$f$$

is not balanced.

Application on 4-bit S-boxes. From [LP07], it is known that the optimal 4-bit S-boxes can be derived from 16 representative S-boxes of CCZ equivalence through affine equivalence. By applying affine transformations to the coordinate functions of these 16 optimal S-boxes, it is observed that each coordinate function of an optimal 4-bit S-box must contain quadratic terms. Therefore, it is evident that a structure where  $g_1$ , i.e.  $f: V \xrightarrow{\widetilde{g}} t_m \xrightarrow{g_1} t_{m+1} = f(V = \{x_0, \cdots, x_{n-1}\})$  ( $g_1$  is a linear component) cannot construct a second balanced Boolean function where  $t_m$  is the first balanced Boolean function with algebraic degree  $l(l \geq 2)$ . This is because either  $t_{m+1}$  lacks quadratic terms or  $t_m + t_{m+1}$  lacks quadratic terms. Property 1 and 3 shows that the second balanced Boolean function cannot be obtained by adding only one nonlinear gate with 2 inputs. What's more, we found that only adding one nonlinear gate with 3 inputs or only adding two nonlinear gates (with 2 or 3 inputs) cannot reach the second balanced Boolean function

when the cost of  $\widetilde{g}$  does not exceed 3 GE. And if only using nonlinear gates, two balanced Boolean functions cannot be obtained under the combined gates with a cost not exceeding 5 GE.

Thus, the optimal way to construct a second coordinate function is that if and only if  $g_0$  is a nonlinear gate and  $g_1$  is a linear gate in  $f: V \xrightarrow{\widetilde{g}} t_m \xrightarrow{g_1} t_{m+1} \xrightarrow{g_2} t_{m+2} = f(V = \{x_0, \cdots, x_3\})$  where  $Pr(t_m = 0) = \frac{1}{2}$  and the cost of  $\widetilde{g}$  is 3 GE. From the perspective of area optimization, constructing two balanced Boolean functions requires at least 2 nonlinear gates and 2 linear gates. On this basis, constructing the other two coordinate functions requires at least 2 additional nonlinear gates. Using this combination of gates as a constraint in the model described in Section 4, we found that no such 4-bit S-box exists. Therefore, constructing a 4-bit S-box requires at least one more gate or replacing one of the nonlinear gates with a linear gate. The minimum area for 4 nonlinear gates and 2 linear gates was found to be 8 GE. Adding at least one more gate or replace one nonlinear gate results in a total minimum area of 9 GE. Hence, we roughly tightened the lower bound for the minimum area construct a 4-bit S-box to be 9 GE if only 2-input and 3-input logic gates are used.

## 4 Improved Automatic Search Model Considering Multiple Cryptographic Properties and Implementation Cost Simultaneously

Using the Prim-Like greedy algorithm, we explore the upper bound of the minimum area for an S-box under specific cryptographic properties, as well as study the lower bound of the area for bijective S-boxes in Section 3. In order to further determine the minimum area for an S-box with given cryptographic properties, we first propose an improved automatic search method to construct S-boxes under certain cryptographic properties in Section 4.1. Then we propose an improved optimization method for S-boxes in Section 4.2. Finally in Section 4.3, we combine these two models above which can take multiple cryptographic properties and area, gate depth into consideration simultaneously.

# 4.1 Improved Automatic Search Method to Construct S-boxes under Certain Cryptographic Properties

#### 4.1.1 Original model in [LMC<sup>+</sup>22]

In [LMC<sup>+</sup>22], Lu et al. constructed the STP-based automatic S-box search by first determining the constraints of the S-boxes cryptographic properties in the CVC language format, including differential uniform  $\mathcal{U}(S)$ , linearty  $\mathcal{L}(S)$ , frequency of  $\mathcal{U}(S)$  and  $\mathcal{L}(S)$ , bijectivity, fix point and so on. According to Definition  $1 \sim 4$ ,  $\mathcal{U}(S)$  and  $\mathcal{L}(S)$  in this model are constrained as follows:

$$\delta_S(\alpha, \beta) \leq \mathcal{U}(S),$$

$|\lambda_S(\alpha, \beta) - 2^{n-1}| \leq \mathcal{L}(S).$

To obtain  $\delta_S(\alpha, \beta)$  and  $\lambda_S(\alpha, \beta)$ , we need to traverse the constraints across the entire DDT and LAT under  $(\alpha, \beta)$ :

$$\text{IsTrue}_{DDT}(\alpha,\beta,x) = \begin{cases} 1, & if \ S(x \oplus \alpha) = S(\alpha) \oplus \beta, \\ 0, & others. \end{cases}$$

$$\text{IsTrue}_{LAT}(\alpha,\beta,x) = \begin{cases} 1, & if \ \alpha \cdot x \oplus \beta \cdot S(x) = 0, \\ 0, & others. \end{cases}$$

Then,  $\delta_S(\alpha, \beta)$  and  $\lambda_S(\alpha, \beta)$  are constructed as follows:

$$\delta_S(\alpha, \beta) = \sum_{x=0}^{2^n - 1} \text{IsTrue}_{DDT}(\alpha, \beta, x),$$

$$\lambda_S(\alpha, \beta) = \sum_{x=0}^{2^n - 1} \text{IsTrue}_{LAT}(\alpha, \beta, x).$$

For the constraints of other cryptographic properties of an S-box, please refer to [LMC<sup>+</sup>22].

#### 4.1.2 Improved model by considering algebraic degree

Lu et al.'s method can consider many cryptographic properties, but unfortunately, it fails to cover the algebraic degree of an S-box which is also a significant cryptographic property. An S-box's algebraic degree can be get from the ANF expression of the S-box's coordinate functions. However, it is difficult to construct ANF in the SAT model. In this part, we give a method to add the constraints about the algebraic degree into the SAT model via SoP expression of Boolean function.

The definition of SoP expression for Boolean function is defined as follows:

**Definition 11** (SoP expression for Boolean function [Sas12]). Assume  $f(x): \mathbb{F}_2^n \to \mathbb{F}_2$  is a Boolean function, then its SoP expression is:

$$f(x) = \bigvee (f(u) \cdot g_u(x)), \tag{19}$$

where  $g_u(x)$  is the Minterm Boolean function defined as follows:

$$g_u(x) = \prod_{j=0}^{n-1} (x_j + u_j + 1) = \begin{cases} 1, x = u \\ 0, x \neq u, \end{cases}$$

(20)

where  $x = (x_0, x_1, \dots, x_{n-1})$  and  $u = (u_0, u_1, \dots, u_{n-1})$ .

From Definition 11, it is easy to find that there are  $2^n$  different Minterm Boolean function  $g_u(x)$  according to the value of u. Each Minterm  $g_u(x) = 1$  only when x = u. This means that only one of  $2^n$  items  $f(u) \cdot g_u(x)$  in Equation (19) will be 1 for given x, while other items are all zero. As a result, the SoP expression of f(x) can be directly transformed as

$$f(x) = \sum f(u) \cdot g_u(x). \tag{21}$$

Actually, the SoP expression cannot be directly used to constrain the algebraic degree, we need to convert the SoP expression in Equation (21) into the ANF expression. It is achieved by combining Definition 11 and Equations (20) (21) as follows:

$$\begin{split} f(x) &= \bigvee_{u \in \mathbb{F}_2^n} f(u) \cdot g_u(x) \\ &= \sum_{u \in \mathbb{F}_2^n} f(u) \cdot \prod_{j=0}^{n-1} (x_j + u_j + 1). \\ &= \sum_{u \in \mathbb{F}_2^n} (f(u) \cdot \sum_{v \in \mathbb{F}_2^n} ((1 + u_0)^{\overline{v_0}} \cdot (1 + u_1)^{\overline{v_1}} \cdots (1 + u_{n-1}^{\overline{v_{n-1}}})) \cdot x_0^{v_0} x_1^{v_1} \dots x_{n-1}^{v_{n-1}}) \\ &= \sum_{u \in \mathbb{F}_2^n} (f(u) \cdot \sum_{v \in \mathbb{F}_2^n} \alpha_v^u \cdot x_0^{v_0} x_1^{v_1} \dots x_{n-1}^{v_{n-1}}) \\ &= (\sum_{u \in \mathbb{F}_2^n} f(u) \cdot \alpha_{2^n - 1}^u) \cdot x_0 \cdots x_{n-1} + \dots + (\sum_{u \in \mathbb{F}_2^n} f(u) \cdot \alpha_1^u) \cdot x_3 + (\sum_{u \in \mathbb{F}_2^n} f(u) \cdot \alpha_0^u), \end{split}$$

where  $\alpha_v^u = (1 + u_0)^{\overline{v_0}} \cdot (1 + u_1)^{\overline{v_1}} \cdots (1 + u_{n-1}^{\overline{v_{n-1}}}).$

Until now, all coefficients in ANF of f(x), which are  $\sum f(u) \cdot \alpha_{2^n-1}^u$ ,  $\sum f(u) \cdot \alpha_{2^n-2}^u$ ,  $\cdots$ ,  $\sum f(u) \cdot \alpha_0^u$ , can be expressed into SAT model since all  $\alpha_v^u$  ( $v \in \mathbb{F}_2^n$ ) can be pre-computed. If we require the algebraic degree of f(x) at least d, then at least one coefficient  $\{wt(v) \geq d \mid \sum f(u) \cdot \alpha_v^u\}$  is not zero. In other word,

$$\begin{cases} \sum_{wt(v)>d} (f(u) \cdot \alpha_v^u) = 0, \\ \sum_{wt(v)=d} (f(u) \cdot \alpha_v^u) \ge 1. \end{cases}$$

(22)

Actually an S-box:  $\mathbb{F}_2^n \to \mathbb{F}_2^n$  can be regarded as a vectorial Boolean function  $(f_0(x), \dots, f_{n-1}(x))$ . To set the algebraic degree of an S-box as d is to set the algebraic degree of at least one coorinate function as d.

**Algorithm 2:** Improved automatic search model for n-bit S-boxes under certain cryptographic properties.

```

Input: \mathcal{U}(S), \mathcal{L}(S), \deg(S) = d, pre-computed \alpha[\mathbf{u}][\mathbf{v}]

Output: CVC-based search model.

1 for in \leftarrow 0 to 2^n - 1 do

for out \leftarrow 0 to 2^n - 1 do

for v \leftarrow 0 to 2^n - 1 do

3

ASSERT(IF\ y_0^{v\oplus in}@\cdots @y_{n-1}^{v\oplus in}=y_0^v@\cdots y_{n-1}^v\oplus out\ THEN

IsTrue_{DDT}(in, out, v) = 1 \ ELSE \ IsTrue_{DDT}(in, out, v) = 0);

ASSERT(IF\ in \cdot v = out \cdot y_0^v @ \cdots @ y_{n-1}^v THEN

IsTrue_{LAT}(in, out, v) = 1 \ ELSE \ IsTrue_{LAT}(in, out, v) = 0);

ASSERT(\delta_{S}[in][out] = \sum_{v=0}^{2^{n}-1} \text{IsTrue}_{DDT}(in, out, v));

ASSERT(\lambda_{S}[in][out] = \sum_{v=0}^{2^{n}-1} \text{IsTrue}_{LAT}(in, out, v));

ASSERT(\delta_{S}[in][out] \leq \mathcal{U}(S));

6

7

ASSERT(2^{n-1} - \mathcal{L}(S) \le \lambda_S[in][out] \le 2^{n-1} + \mathcal{L}(S));

10 for X \leftarrow 0 to 2^n - 1 do

x_0@x_1@\cdots @x_{n-1} = X;

11

ASSERT(X \neq y_0^X@y_1^X@\cdots @y_{n-1}^X); // \text{ without fixed point}

for Z \leftarrow X + 1 to 2^n - 1 do

13

15 // Constrain the algebraic degree of an S-box to be d.

16 ASSERT(\sum_{i=0}^{n-1} \sum_{u=0}^{2^{n}-1} \sum_{wt(v)=d} (y_i^u \cdot \alpha[u][v]) \ge 1);

17 for i \leftarrow 0 to n-1 do

ASSERT(\sum_{u=0}^{2^{n}-1}\sum_{wt(v)>d}(y_{i}^{u}\cdot\alpha[u][v])=0);

```

For example, assume the algebraic degree of one coordinate function f of a 4-bit S-box to be 3. In the ANF of f(x), we only need to focus on the coefficients of the cubic monomials, i.e., the coefficients of  $x_0x_1x_2$ ,  $x_0x_1x_3$ ,  $x_0x_2x_3$ ,  $x_1x_2x_3$ , which are  $\sum_{u \in \mathbb{F}_2^n} f(u)\alpha_{14}^u$ ,  $\sum_{u \in \mathbb{F}_2^n} f(u)\alpha_{13}^u$ ,  $\sum_{u \in \mathbb{F}_2^n} f(u)\alpha_{11}^u$  and  $\sum_{u \in \mathbb{F}_2^n} f(u)\alpha_1^u$  respectively. Since for an n-bit Boolean function, each ANF expression of  $g_u(x)$  can be computed. By expanding all  $g_u(x)$ , we obtain all of  $\alpha_{14}^u$ ,  $\alpha_{13}^u$ ,  $\alpha_{11}^u$ ,  $\alpha_{11}^v$ ,  $\alpha_{11}^v$ , which are shown in Table 8.

Finally, we constrain the algebraic degree of one coordinate function of an S-box to be 3, that is:

$$\sum_{u \in \mathbb{F}_2^n} f(u)\alpha_{14}^u + \sum_{u \in \mathbb{F}_2^n} f(u)\alpha_{13}^u + \sum_{u \in \mathbb{F}_2^n} f(u)\alpha_{11}^u + \sum_{u \in \mathbb{F}_2^n} f(u)\alpha_7^u \ge 1.$$

(23)

| ľ | olean function.       |   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

|---|-----------------------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

|   | $u 	ext{ of } g_u(x)$ | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|   | $\alpha_{14}^u$       | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1  | 0  | 1  | 0  | 1  | 0  |

|   | $\alpha_{13}^u$       | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0  | 0  | 1  | 1  | 0  | 0  |

|   | $\alpha_{11}^u$       | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1  | 1  | 0  | 0  | 0  | 0  |

|   | $\alpha_7^u$          | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

**Table 8:** Coefficient of each cubic monomial in the ANF expansion of  $g_u(x)$  for a 4-bit Boolean function.

Combining the new findings on algebraic degree and original model in [LMC<sup>+</sup>22], we propose an improved automatic search model based on SAT, which is shown in Algorithm 2.

#### 4.2 Improved Optimization Implementation Method for Given S-boxes

#### 4.2.1 Original model in [LWH+21]

The model proposed in [LWH<sup>+</sup>21], built upon the Gate Count Complexity model from [Sto16], optimizes the area cost of an S-box by assigning a weight to each gate corresponding to its area. This approach enables to calculate the minimum area for a given S-box and support 4-input gates. Assume there are k gates in total, the expressions for four possible inputs of the i-th (i = 0, 1, ..., k - 1) gate can be written as:

$$\begin{cases}

q_{4i} &= a_0^i \cdot x_0 + \dots + a_{n-1}^i \cdot x_{n-1} + a_n^i \cdot t_0 + \dots + a_{n+i-1}^i \cdot t_{i-1}, \\

q_{4i+1} &= b_0^i \cdot x_0 + \dots + b_{n-1}^i \cdot x_{n-1} + b_n^i \cdot t_0 + \dots + b_{n+i-1}^i \cdot t_{i-1}, \\

q_{4i+2} &= c_0^i \cdot x_0 + \dots + c_{n-1}^i \cdot x_{n-1} + c_n^i \cdot t_0 + \dots + c_{n+i-1}^i \cdot t_{i-1}, \\

q_{4i+3} &= d_0^i \cdot x_0 + \dots + d_{n-1}^i \cdot x_{n-1} + d_n^i \cdot t_0 + \dots + d_{n+i-1}^i \cdot t_{i-1}.

\end{cases} (24)$$

where  $x_i$  (i = 0, 1, ..., n - 1) denotes the *i*-th input bit of S-box, and  $t_i$  (i = 0, 1, ..., k - 1) denotes the output bit of the *i*-th gate.

Each input bit of the *i*-th gate comes either from one input bit of S-box or one output bit from any preceding gate. Thus, in each expression for  $q_{4i}$ ,  $q_{4i+1}$ ,  $q_{4i+2}$ ,  $q_{4i+3}$ , only one coefficient is 1, other coefficients are all 0, i.e. that is

$$\begin{cases}

\sum_{j=0}^{n+i-1} a_j^i &= 1, \\

\sum_{j=0}^{n+i-1} b_j^i &= 1, \\

\sum_{j=0}^{n+i-1} c_j^i &= 1, \\

\sum_{j=0}^{n+i-1} d_j^i &= 1.

\end{cases}$$

(25)

Within the search model, we can collect constraints between the inputs and output of every logic gate under  $\{\mathcal{G}_1, \mathcal{G}_2, \mathcal{G}_3, \mathcal{G}_4\}$  using the following formula:

$$t_{i} = \beta_{0}^{i} \cdot q_{4i} \cdot q_{4i+1} \cdot q_{4i+2} \cdot q_{4i+3} + \beta_{0}^{i} \cdot q_{4i} \cdot q_{4i+1} \cdot q_{4i+2} + \beta_{0}^{i} \cdot q_{4i} \cdot q_{4i+1} \cdot q_{4i+3} + \beta_{0}^{i} \cdot q_{4i+2} \cdot q_{4i+3} + \beta_{0}^{i} \cdot q_{4i+2} + \beta_{0}^{i} \cdot q_{4i+3} + \beta_{1}^{i} \cdot q_{4i} \cdot q_{4i+1} \cdot q_{4i+2} + \beta_{2}^{i} \cdot q_{4i+1} + \beta_{2}^{i} \cdot q_{4i} \cdot q_{4i+2} + \beta_{2}^{i} \cdot q_{4i+1} \cdot q_{4i+2} + \beta_{2}^{i} \cdot q_{4i} + \beta_{2}^{i} \cdot q_{4i+1} + \beta_{2}^{i} \cdot q_{4i+1} + \beta_{3}^{i} \cdot q_{4i+1} + \beta_{3}^{i} \cdot q_{4i+2} + \beta_{4}^{i} \cdot q_{4i} \cdot q_{4i+1} + \beta_{5}^{i} \cdot q_{4i+1} + \beta_{6}^{i} \cdot q_{4i} + \beta_{7}^{i},$$

$$(26)$$

where the coefficients  $(\beta_0^i, \beta_0^i, \dots, \beta_7^i)$  determine the type of the *i*-th gate and its area. The corresponding relationship between  $(\beta_0^i, \beta_0^i, \dots, \beta_7^i)$  and logic gates is shown in Table 9.

In the end, each of n output bits  $y_i$  (i = 0, 1, ..., n - 1) of S-box also comes either from one input bit of S-box or one output bit from any preceding gate. Thus, the expression for

| Logic Gates | $\beta_0^i$ | $\beta_1^i$ | $\beta_2^i$ | $\beta_3^i$ | $\beta_4^i$ | $\beta_5^i$ | $\beta_6^i$ | $\beta_7^i$ | Cost/GE |

|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|---------|

| NOT         | 0           | 0           | 0           | 0           | 0           | 0           | 1           | 1           | 0.67    |

| XOR         | 0           | 0           | 0           | 0           | 0           | 1           | 0           | 0           | 3.00    |

| XNOR        | 0           | 0           | 0           | 0           | 0           | 1           | 0           | 1           | 3.00    |

| NOT         | 0           | 0           | 0           | 0           | 0           | 1           | 1           | 1           | 0.67    |

| AND         | 0           | 0           | 0           | 0           | 1           | 0           | 0           | 0           | 1.33    |

| NAND        | 0           | 0           | 0           | 0           | 1           | 0           | 0           | 1           | 1.00    |

| OR          | 0           | 0           | 0           | 0           | 1           | 1           | 0           | 0           | 1.33    |

| NOR         | 0           | 0           | 0           | 0           | 1           | 1           | 0           | 1           | 1.00    |

| AND3        | 0           | 1           | 0           | 0           | 0           | 0           | 0           | 0           | 1.33    |

| NAND3       | 0           | 1           | 0           | 0           | 0           | 0           | 0           | 1           | 1.67    |

| OR3         | 0           | 1           | 1           | 0           | 0           | 0           | 0           | 0           | 1.33    |

| NOR3        | 0           | 1           | 1           | 0           | 0           | 0           | 0           | 1           | 1.67    |

| XOR3        | 0           | 0           | 0           | 1           | 0           | 0           | 0           | 0           | 4.67    |

| XNOR3       | 0           | 0           | 0           | 1           | 0           | 0           | 0           | 1           | 4.67    |

| MAOI1       | 1           | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 2.67    |

| MOAI1       | 1           | 0           | 0           | 0           | 0           | 0           | 0           | 1           | 2.00    |

**Table 9:** Corresponding relationship between the values of  $(\beta_0^i, \beta_1^i, \dots, \beta_7^i)$  and logic gates in [LWH<sup>+</sup>21].

each  $y_i$  can be written as:

$$\begin{cases}

y_0 = a_0^{k,0} \cdot x_0 + \dots + a_{n-1}^{k,0} \cdot x_{n-1} + a_n^{k,0} \cdot t_0 + \dots + a_{n+k-1}^{k,0} \cdot t_{k-1}, \\

y_1 = a_0^{k,1} \cdot x_0 + \dots + a_{n-1}^{k,1} \cdot x_{n-1} + a_n^{k,1} \cdot t_0 + \dots + a_{n+k-1}^{k,1} \cdot t_{k-1}, \\

\vdots & \vdots \\

y_{n-1} = a_0^{k,n-1} \cdot x_0 + \dots + a_{n-1}^{k,n-1} \cdot x_{n-1} + a_n^{k,n-1} \cdot t_0 + \dots + a_{n+k-1}^{k,n-1} \cdot t_{k-1}.

\end{cases} (27)$$

Similar to add constraints on coefficients as that in Equation (25), here we can describe the constraints on output bits as well.

Additionally, the constraints on area should be added into the model. since all logic gates are multiples of 0.33 GE, the proportion of area for different logical gates is used to measure the area in our model for the sake of simplicity and convenience. For example, the area of AND in the model is set to be 4, since its actual area is 4 times of 0.33GE. By summing up the area of all k logic gates and ensuring it is no more than the target area  $Cost_{target}$ , we can find the optimized implementation for a given S-box under such target area. Furthermore, by gradually reducing the target area, we can find the minimum-area implementation for a given S-box. The corresponding constraints in the model are as follows.